这部分介绍的IP具有普适性,即使在进行其它设计时也极有可能有应用,属于基础中的基础。

1.ZYNQ7 Processing System

通过对该 IP 进行功能配置,可以自定义Soc系统实现“量身定制”的效果,ZYNQ-7000系列内置双ARM-A9核,资源十分丰富,因此在这里只取我们用到的模块进行详细介绍。

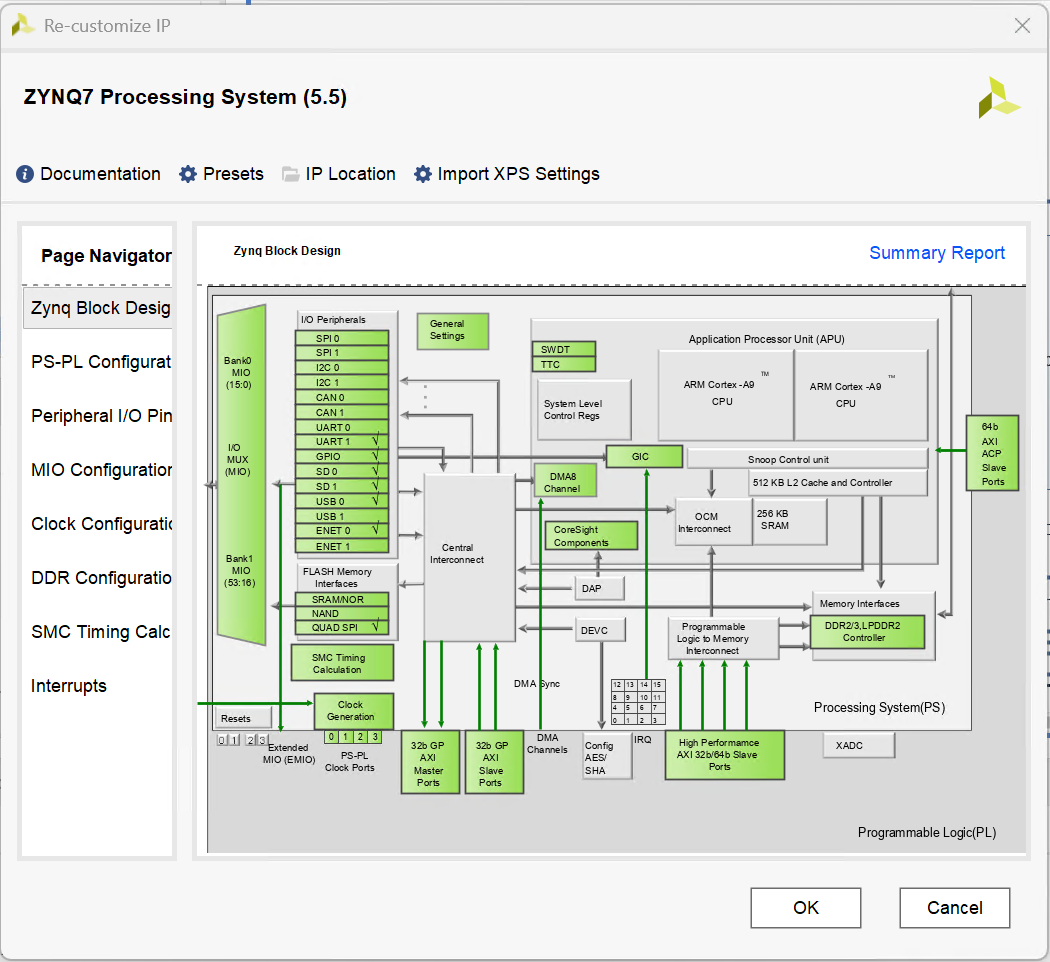

首先打开该 IP 核,映入眼帘的是如下配置:

ZYNQ-7000 IP配置

在该项目中,我们主要应用了片上的AXI-GP、HP接口进行数据传输,DDR3做缓存,PS-PL中断处理,串口输出调试,PS-PL端时钟配置,下面分别进行详细介绍:

1.1 AXI HP/GP Interface

AXI HP/GP Interface配置

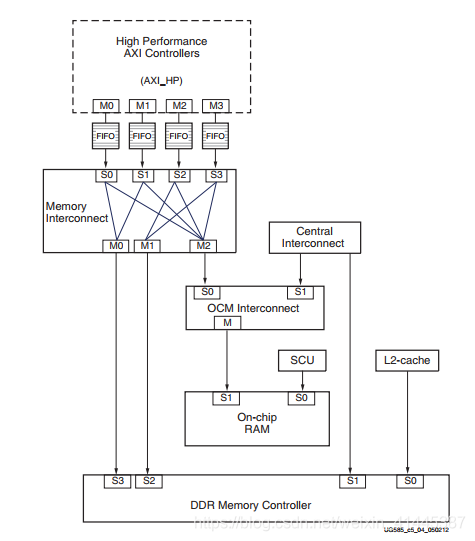

从中可以看出,对于GP(general purpose)通用目的接口,有两主两从共四个接口;对于HP(high-performance purpose)高性能接口,四接口均为从接口。GP接口直接连接到的是中央互联区(central interconnect),然后由中央互联区再连接到OCM interconnect和存储器接口上;而HP接口直接连接到的是OCM interconnect和存储器接口。所以对于GP接口,通常使用他进行控制配置;而对于HP接口,通常使用它进行数据传输交互。

在本工程中,我们使用HP接口实现DDR存储器与ZYNQ的高效数据交互,采用GP接口进行轻量传输,如寄存器配置、GPIO读写等。

4个AXI HP接口为PL的主机提供了DDR和OCM存储器的高带宽的数据路径。每个HP接口包括两个的FIFO缓存,用于读写传输。PL到内存互连高速AXI HP端口路由连接到两个DDR内存端口和一个OCM存储器端口。AXI HP接口也被称为AFI (AXI FIFO接口),以强调它们的缓冲功能。

AXI HP接口主要特点

AXI HP接口框图

可以实现32或64位数据位宽的主接口(每个端口独立编程)。

在32位接口模式下,可以进行动态配置位为64位,以实现对齐传输,通过AxCACHE [1]可以进行控制。

在32位接口模式下,为未对齐的32位传输自动扩展到64位。

可编程的写命令释放阈值。

PL和PS之间的所有AXI接口的异步时钟域交叉。

使用1kb (128 × 64位)数据缓存FIFO来平滑“长延迟”传输,用于读写。

从PL端口提供QoS信令。

命令和数据FIFO填充级计数可用于PL端。

支持标准AXI 3.0接口。

可编程命令下发到互连,分别用于读和写命令。

14到70个指令范围的高性能从接口读接受能力。(取决于突发长度)

8到32个指令范围的高性能从接口写接受能力。(取决于突发长度)

AXI_GP接口直接连接到主互连和从互连的端口,没有任何额外的FIFO缓冲,不像AXI_HP接口使用FIFO缓冲以提高性能和吞吐量。因此,性能受到主互连端口和从互连端口的限制。这些接口仅用于通用用途,并不是为了实现高性能。主机接口具有发起读写的权限,ARM 可以利用两个 AXI GP 主机接口主动访问 PL 逻辑,其实就是把 PL 映射到某个地址,读写 PL 寄存器。

AXI GP接口主要特点

支持标准AXI协议。

数据总线宽度只有32位。

主端口ID位宽为12位。

主端口发送能力:8位读,8位写。

从端口ID位宽为6位。

从端口接受能力:8位读,8位写。

1.2 DDR3

对于图像处理等大数据量的数据交互来说,PL端的BRAM毕竟容量有限,很难用BRAM作为两者间的数据缓存器。对于本项目要实现的Yolo v5应用来说,利用DDR3作为PS端与PL端之间交互的数据缓存器是最合适不过的。同时考虑到总线带宽,在实际应用时最好采用AXI-Stream而不是轻量级的AXI-Lite,这一点后面会进行详细说明。

ZYNQ 7000系列分别内置两片512MB PL DDR3与两片512MB PS DDR3,其中PL端DDR3可以通过MIG(Memory Interface Generator) IP进行配置,PS端DDR3则只需enable ddr并正确配置型号等参数即可顺利驱动,该IP会将我们输入输出的数据自动转为符合ddr的读写时序,并通过自带的DDR Interface实现交互。

DDR3配置

从中不难看出,DDR3的型号为 MT41K256M16 RE-125 ,通过该命名我们也可以得知关于该DDR3的一系列信息,有助于我们确定配置参数:

MT41K:Micron Technology公司生产的DDR3 SDRAM芯片系列的型号。

256M:芯片的容量是256Mb(兆位),即32MB(兆字节)。

16:内存芯片的位宽,表示单个存储单元的位数,通常为8位或16位。

RE-125:最大读写频率800MHz(1G/125*100)

关于ddr3的读写时序,会在后面进行详细说明,这里仅介绍相关配置,以成功驱动为主。

1.3 PS-PL中断处理

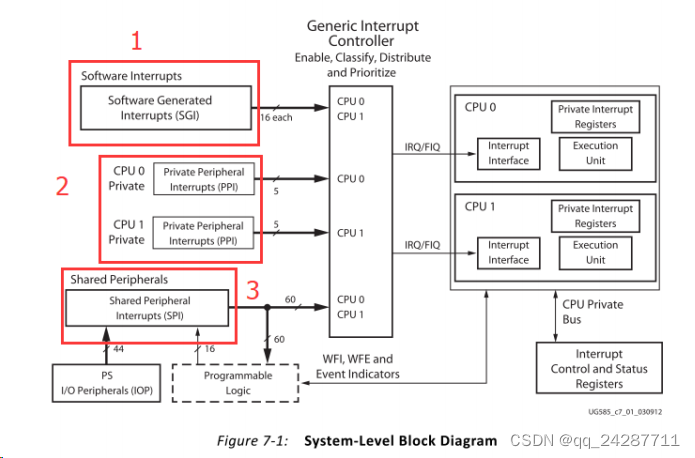

通过用户手册不难得知,在ZYNQ系统中,中断可以分为三大类,其架构图如下所示:

SGI(Software Generated Interrupt),软件生成的中断,共 16 个端口,中断号0~15;

PPI(Private Peripheral Interrupt

SPI(Shared Peripheral Interrupt),共享外设中断,来自于 44 个 PS 端的IO 外设以及 16 个 PL 端的中断,中断号32~95。

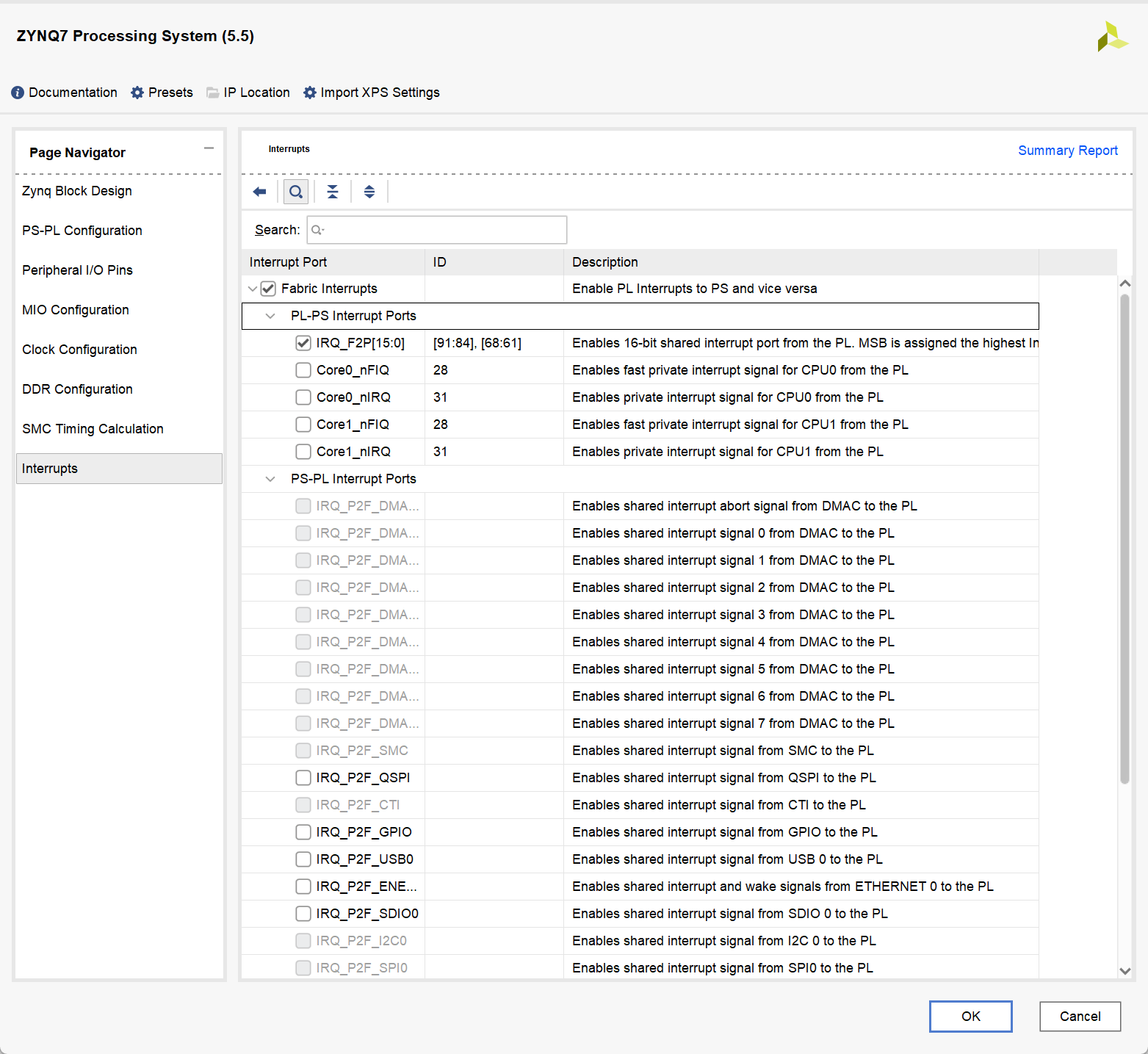

中断相关配置如下图所示,作为开发者,我们只能对第三类SPI中断进行配置,而从中可以看出,该中断子系统又可以分为两种,分别是PL-PS Interrupt和PS-PL Interrupt。

在本项目中我们只启用前者,因此对后者仅作简单介绍。

Interrupt配置

PL-PS Interrupt

顾名思义,是由PL端发出PS端接收的中断信号,PS 最大可以接收 16 个来自 PL 的中断信号,都是上升沿或高电平触发。相应地,在PS中启用GIC(Generic Interrupt Controller)或使用Zynq的专用中断控制器。并编写中断处理程序,处理来自PL的中断信号,通过中断程序与PL进行进一步的数据交换。

PS-PL Interrupt

顾名思义,是由PS端发出PL端接收的中断信号,从中断配置图中我们也可看出可以配置中断的资源十分丰富,需要我们根据实际应用自己决定,中断信号可以通过 AXI 控制总线或专用信号直接触发。通常情况下,可以在PS端通过中断信号告诉PL可以开始执行某些操作,从而实现特定逻辑的优先处理。

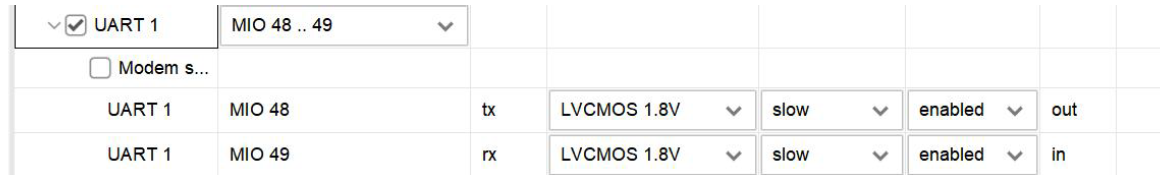

1.4 ZYNQ的串口配置

ZYNQ的串口同样具备STM32中的各种功能,不过在这里我们只是利用它输出一些调试结果,所以进行最基本的配置即可,软件端Xilinx的官方库文件会帮我们处理好剩下的一切

UART配置

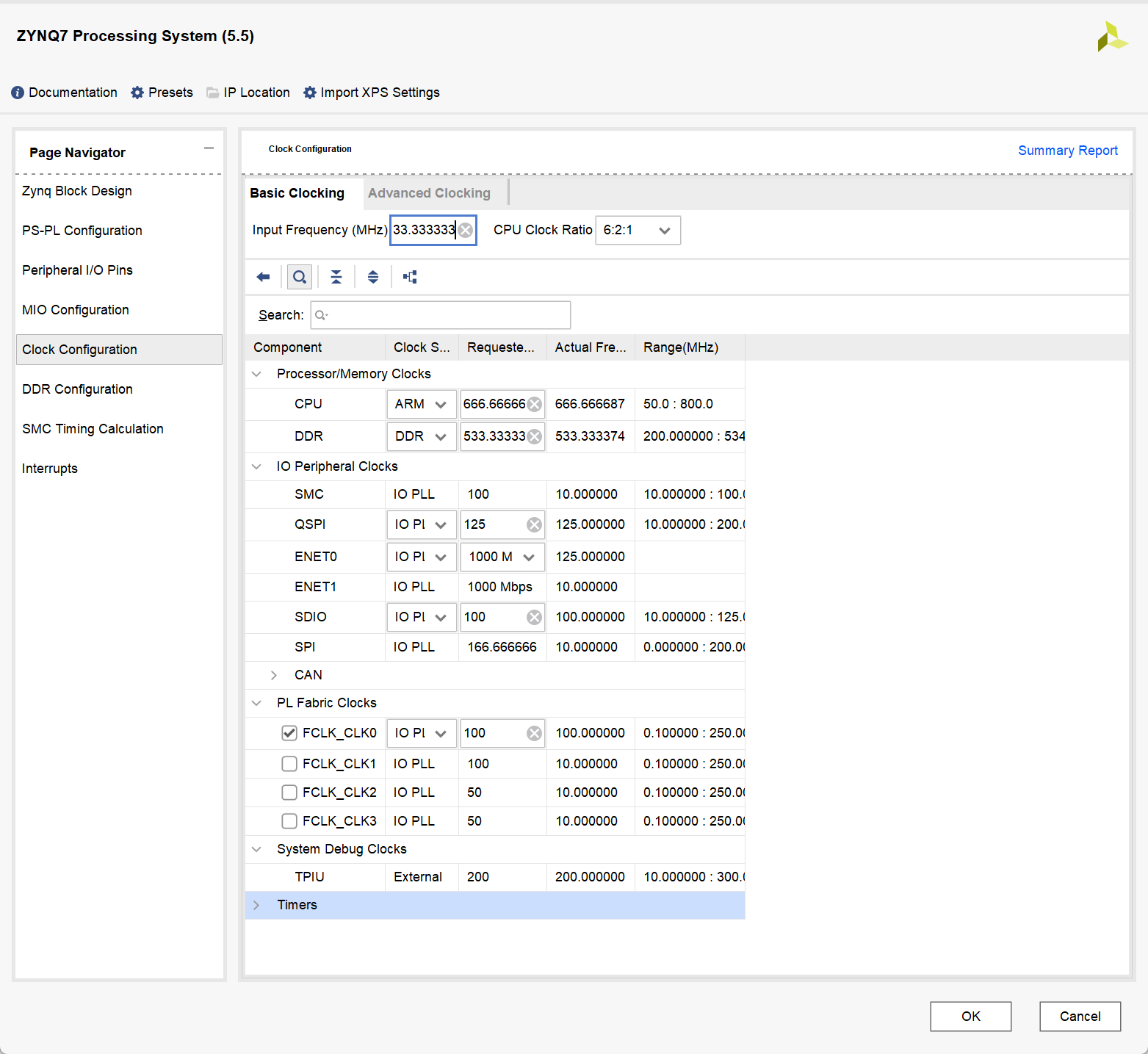

1.5 PL-PS端时钟设置

PS 时钟子系统生成的所有时钟都来自三个可编程 PLL 之一:CPU、DDR 和 I/O。正常模式下,PLL被启用,并由PS_CLK时钟管脚驱动。在Bypass模式中,PS_CLK代替PLL向各时钟发射器提供时钟源。在这里我们给出如下配置并进行简单说明。

Clock System配置

其中Input Frequency默认为33.333MHz,由内部晶振产生,CPU Clock Ratio默认为6:2:1,实际上代表着一种工作模式。

DDR Clock

DDR_3x与DDR_2x是相互独立的。DDR_3x时钟域包括DDR内存控制器;DDR_2x时钟域主要用于AXI_HP接口和互连。

PL Clock

PS向PL提供四个时钟,分别是PL_FCLK 0、PL_FCLK 1、PL_FCLK 2、PL_FCLK 3。四个时钟来自 PS 中的PLL可单独选择。用户可根据需求设置时钟频率。

同时对每个PL时钟,也可以设置其相应的复位信号是否使能。

IOP Module Clock

IOP 模块时钟(用于内部控制器逻辑)可以由时钟子系统或在某些情况下由 IOP 的外部接口生成。 在所有情况下,IOP 的控制和状态寄存器均由其 AMBA 接口时钟 (CPU_1x) 提供时钟。

2.AXI Interconnect

AXI InterConnect可以对AXI总线进行管理,支持多个主机采用AXI总线访问从机,或者一个主机访问多个从机。真正实现了总线通信,N Master模块与M Slave模块的通信,减少了相互间通信的复杂度,内部实现时钟域转换,不需要外部的过度干预,内部可实现FIFO等,免去了很多场景下需要FIFO,Register,位宽转换,协议转换的需求。

该IP核最多可以支持16个主设备、16个从设备,如果需要更多的接口,可以多加入几个IP核,通常该IP核在Block Design中用的比较多,下面介绍一下在Block Design中的用法。在Block Design中通常会简化IP核的用法,但是可以自动布线。对于AXI这种信号比较多的信号,在Block Design中也更方便一些。

为了便于总线管理,在应用时通常设置两个AXI Interconnect模块,一个一主多从一个一从多主,实现ZYNQ ARM核与多外设的交互。

单个主机访问多个从机

单个主机访问多个从机的原理是采用为从机的AXI总线分配不同的地址,这样主机通过访问不同的地址分区来访问不同的从机。

单个主机访问多个从机

多个主机读写一个从机是通过主机的ID号不同来实现的,每个主机具有不同的ID号,内部通过读写的时候地址会把这个主机号加上,代表哪个主机进行访问,传回的数据就传到相应的主机。当主机同时访问从机时,还可以设置主机的优先级进行判别哪一个主机进项访问。

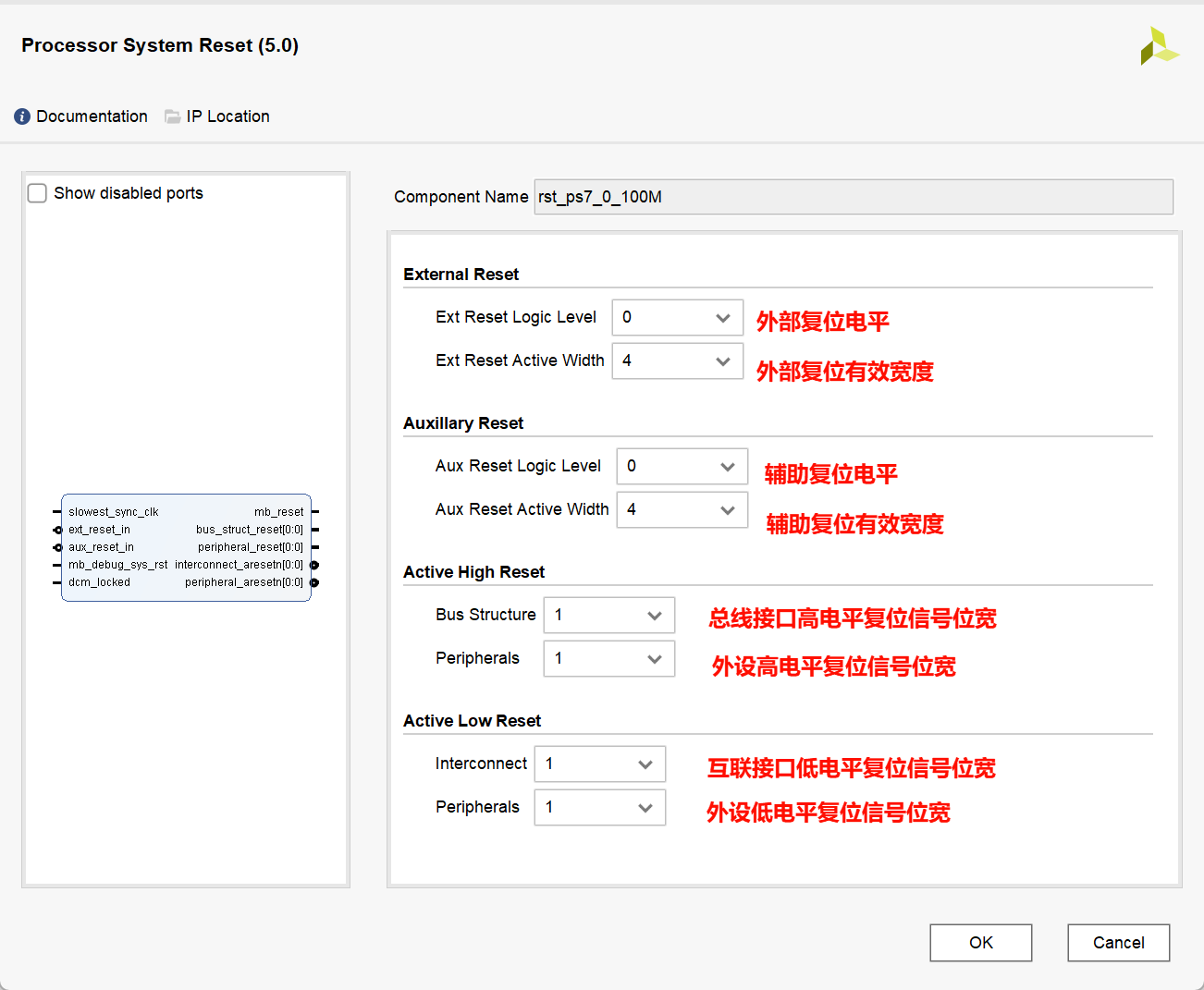

3.Processor System Reset

该复位模块允许客户通过设置某些参数来启用/禁用功能,从而根据自己的应用来定制设计。主要支持下列功能:

使异步外部复位(External Reset)信号与时钟同步

使异步辅助复位(Auxillary Reset)信号与时钟同步

可选外部/辅助复位信号是低电平有效还是高电平有效

可选复位信号需持续的最小脉宽

可选负载均衡

DCM锁定输入

生成上电复位信号

IP核配置相关说明

IP核接口相关说明

| 名称 | 方向 | 位宽 | 有效电平 | 说明 |

|---|---|---|---|---|

| slowest_sync_clk | I | 1 | - | 最慢同步时钟 |

| ext_reset_in | I | 1 | 可配置,默认低电平有效 | 外部复位 |

| aux_reset_in | I | 1 | 可配置,默认低电平有效 | 辅助复位 |

| mb_debug_sys_rst | I | 1 | 高 | 总线调试复位 |

| dcm_locked | I | 1 | 高 | dcm的locked信号 |

| mb_reset | O | 1 | 高 | 总线复位 |

| bus_struct_reset | O | 1 ~ 8,默认1 | 高 | 总线高电平复位 |

| peripheral_reset | O | 1 ~ 16,默认1 | 高 | 外设高电平复位 |

| interconnect_aresetn | O | 1 ~ 8,默认1 | 低 | 互联低电平复位 |

| peripheral_aresetn | O | 1 ~ 16,默认1 | 低 | 外设低电平复位 |

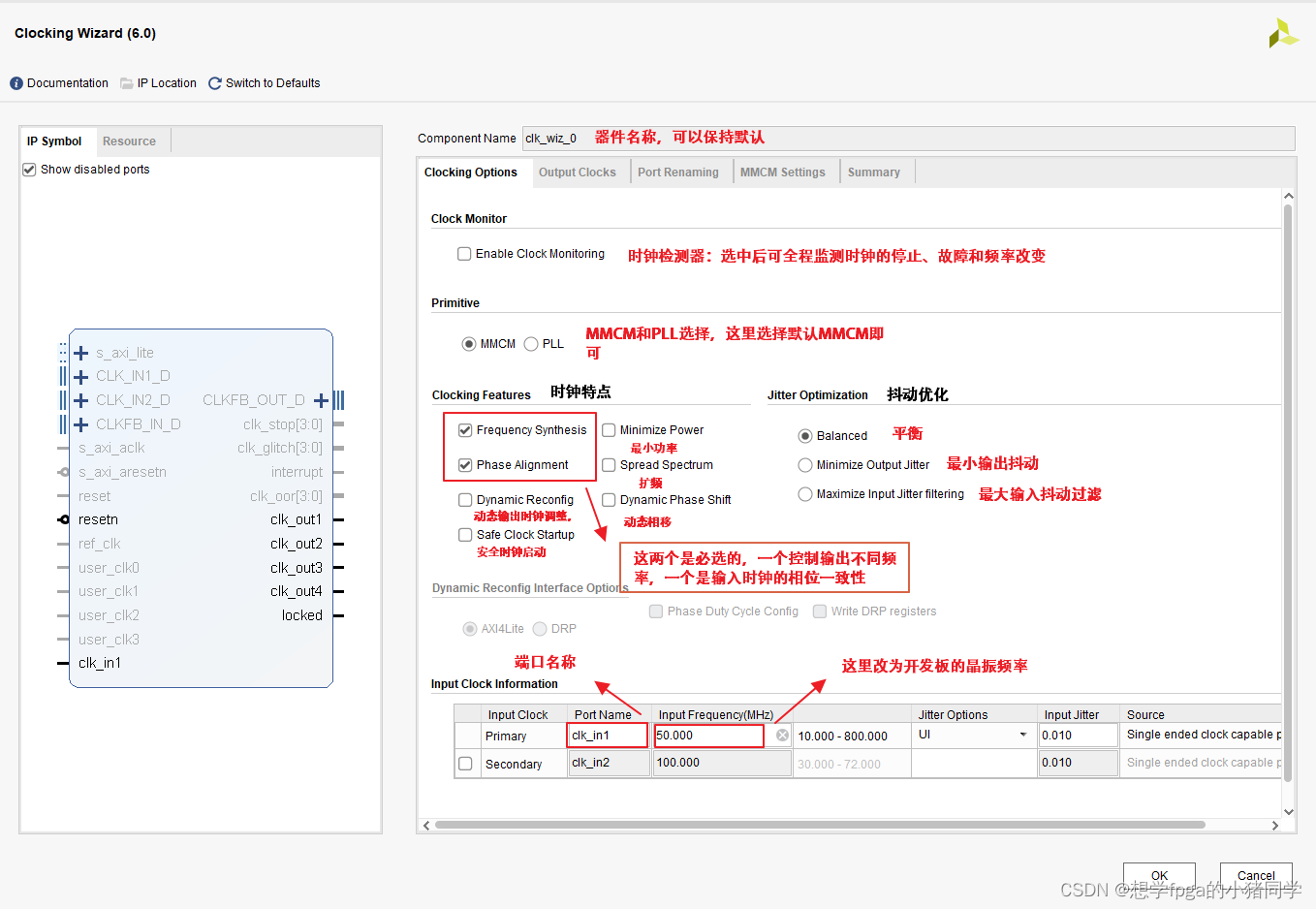

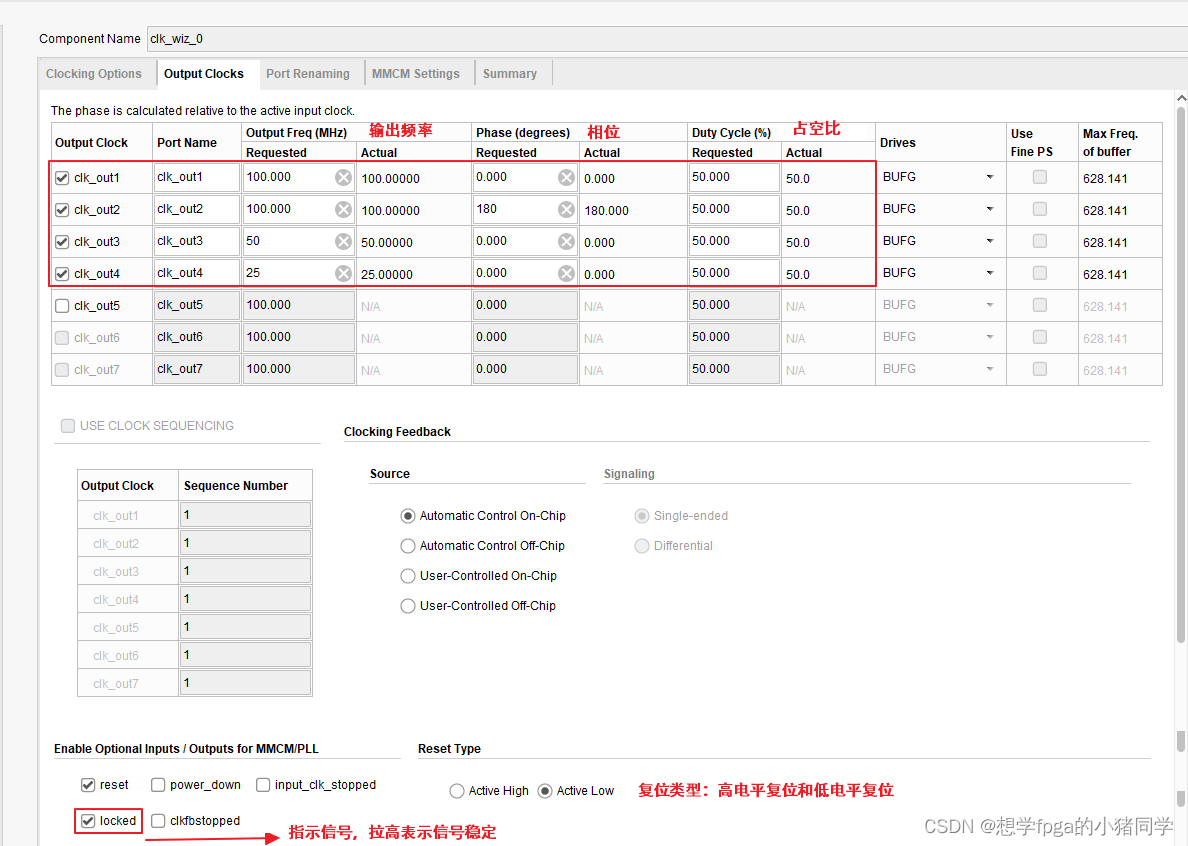

4.Clocking Wizard

这是一个应用十分广泛的时钟管理IP,可以使用户根据自己喜好,根据输入时钟实现倍频、分频、占空比、相位等一系列配置。在本项目中,我们用它产生视频流时序需要的时钟。

IP核配置相关说明

-

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。其具有时钟倍频、分频、相位偏移和可编程占空比的功能。

-

MMCM(Mixed Mode Clock Manager):混合模式时钟管理器, MMCM 功能是 PLL 的超集, 在PLL的基础上加上了相位动态调整功能,因为PLL是模块电路,而动态调相是数字电路,所以叫Mixed Mode。MMCM是在Virtex-6中被引入的,而且Virtex-6中也只有MMCM。